Merge pull request #1 from muhammed-celik/main_ Main

diff --git a/README.md b/README.md index 932ef7f..7bf02e5 100644 --- a/README.md +++ b/README.md

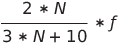

@@ -14,7 +14,44 @@ Overview ======== -TBA +The Turbo Encoder is used for FEC encoding for linear modulation. + +Encoder takes 2 bits of input (namely A and B) and generates 6 bits of output in the form (AB Y1W1 Y2W2) + +First couple of parity bits (Y1W1) are generated from normal ordered input data while second couple of parity bits (Y2W2) are generated from interleaved input data. + +The design involves two paths one of which is used for interleaved input data. + +#### Top-Level Diagram + + +-Input Data is stored at dual channel rams. + +-AGU (Address Generator Unit) generates data indices for interleaving. + +-Pre Encoder unit identifies initial state of the encoder. + +-Encoder Core produces outputs according to the state and the inputs. + +#### Synthesis Report + + +#### Implementation Report + + +-Reports are based on Xilinx Spartan-7 xc7s6ftgb196-1 + + +#### Throughput + + +'N' = input data block size in couple number ranging from 56 to 2396. + +'f' = frequency in Mhz. + +For 50 Mhz clock speed and N = 56, throughput equals 31.5 Mbps. + +For 50 Mhz clock speed and N = 2396, throughput equals 33.3 Mbps. Setup ========

diff --git a/docs/images/encoder_schematic.png b/docs/images/encoder_schematic.png new file mode 100644 index 0000000..71a7722 --- /dev/null +++ b/docs/images/encoder_schematic.png Binary files differ

diff --git a/docs/images/imp_encoder.png b/docs/images/imp_encoder.png new file mode 100644 index 0000000..2bf5bb9 --- /dev/null +++ b/docs/images/imp_encoder.png Binary files differ

diff --git a/docs/images/synt_encoder.png b/docs/images/synt_encoder.png new file mode 100644 index 0000000..1a96099 --- /dev/null +++ b/docs/images/synt_encoder.png Binary files differ