| commit | de2760e9e7a652b5e12debcdd00b0d1ba16b4353 | [log] [tgz] |

|---|---|---|

| author | baburaj2000 <88964390+baburaj2000@users.noreply.github.com> | Sat Oct 23 06:53:57 2021 +0530 |

| committer | GitHub <noreply@github.com> | Sat Oct 23 06:53:57 2021 +0530 |

| tree | 633a785ea1cde7fb76cf9c7c0659950ac0d07002 | |

| parent | 5b43c7117436091b188dbc0f6f8937c0537f0923 [diff] |

Update README.md

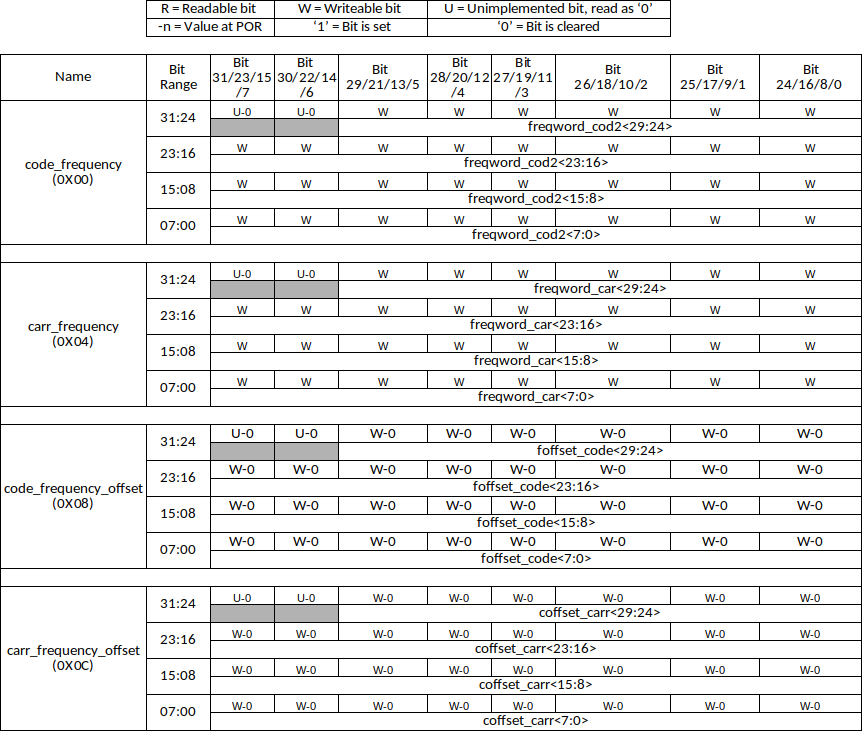

Overview RTL Implementation RTL Verification ASIC Implementation In this proposal, the entire GPS baseband functionality is realized using a combination of custom designed logic functionality GPS Engine (ASIC portion) and the on chip RISCV microprocessor to provide the complete position fix starting from the digitized IF input bits. The signal processing operations in the baseband comprise of dispreading and data demodulation performed on six identical channels followed by psuedo range, and position fix computation. The major part of the signal processing operations for the six channels are carried out in the GPS Engine and the low frequency control tasks and position fix computation tasks are carried out in the RISCV processor.

The Caravel user_proj_example.v has eight instanciation of GPS channel and a I2C Master . The GPS Channel < write the functionality of gps channel> and the I2C Master is used to configure the GPS RF Front End chipset .

The following block diagram shows the internal blocks of single gps channel

The verification environment is shown in the following block diagram . A wishbone bus function model is used to create wishbone write and read transactions .