| # YONGA-Turbo Encoder |

| |

| [](https://opensource.org/licenses/Apache-2.0) [](https://github.com/efabless/caravel_project_example/actions/workflows/user_project_ci.yml) [](https://github.com/efabless/caravel_project_example/actions/workflows/caravel_build.yml) |

| |

| Table of contents |

| ================= |

| |

| - [Overview](#overview) |

| - [Setup](#setup) |

| - [Running Simulation](#running-simulation) |

| - [Hardening the User Project Macro using OpenLANE](#hardening-the-user-project-macro-using-openlane) |

| - [List of Contributors](#list-of-contributors) |

| |

| Overview |

| ======== |

| #### DVB-RCS2 Turbo Encoder |

| |

| Turbo Encoder is used for FEC encoding for linear modulation. |

| |

| Encoder takes 2 bits of input (namely A and B) and generates 6 bits of output in the form (AB Y1W1 Y2W2) |

| |

| First couple of parity bits (Y1W1) are generated from linearly ordered input data while second couple of parity bits (Y2W2) are generated from interleaved input data. |

| |

| The design involves two paths: |

| 1) Linear order path |

| 2) Interleaved path |

| |

| #### Top-Level Diagram |

|  |

| |

| -Input Data is stored at dual channel rams. |

| |

| -AGU's (Address Generator Unit) generate data indices for linearly ordered and interleaved data inputs. |

| |

| -Pre Encoder unit identifies initial state of the encoder. |

| |

| -Encoder Core produces outputs according to the state and the inputs. |

| |

| #### Synthesis Report |

|  |

| |

| #### Implementation Report |

|  |

| |

| -Reports are based on Xilinx Spartan-7 xc7s6ftgb196-1 |

| |

| |

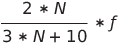

| #### Throughput |

|  |

| |

| 'N' = input data block size in couple number ranging from 56 to 2396. |

| |

| 'f' = frequency in Mhz. |

| |

| For 50 Mhz clock speed and N = 56, throughput equals to 31.5 Mbps. |

| |

| For 50 Mhz clock speed and N = 2396, throughput equals to 33.3 Mbps. |

| |

| Setup |

| ======== |

| |

| TBA |

| |

| Running Simulation |

| ======== |

| |

| TBA |

| |

| Hardening the User Project Macro using OpenLANE |

| ======== |

| |

| TBA |

| |

| List of Contributors |

| ================================= |

| |

| *In alphabetical order:* |

| |

| - Baris Bilgili |

| - Burak Yakup Cakar |

| - Muhammed Celik |